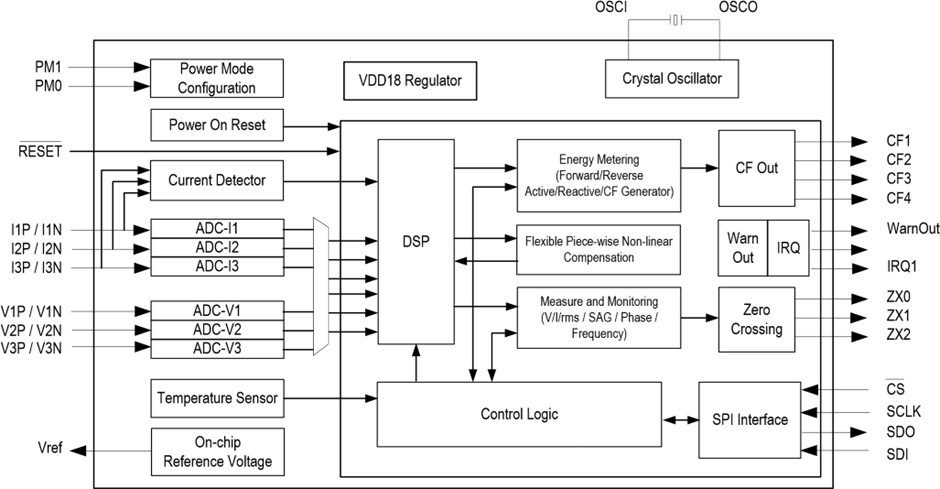

IC의 개요

성능이 우수한 다사의 고성능의 넓은 입력 범위의 에너지 계측용 IC

측정항목 : 유효전력, 무효전력, 피상전력, 전압, 전류의 실효치.

SPI 통신 적용

| Name | Pin No. | I/O | Type | Description |

| Reset | 41 | I | LVTTL | Reset: Reset Pin (active low), 리셋은 액티브 low, low이면 리셋 이 핀과 GND 사이에 0.1uF 캐패시터(필터)와 VDD 사이에는 10kΩ을 연결시킨다. 어플리케이션에서는 MCU의 핀에 직접 연결할 수도 있다. |

| AVDD | 1 | I | Power | AVDD: Analog Power Supply 아날로그 전원 This pin provides power supply to the analog part. This pin should connect to DVDD and be decoupled with a 0.1μF capacitor. 이핀은 아날로그 파트 전원. DVDD에 연결되어야하고 0.1uF 캐패시터로 디커플되어야한다. |

| DVDD | 48 | I | Power | DVDD: Digital Power Supply 디지털 전원 이 핀은 디지털 파트 전원. 10uF, 0.1uF캐패시터를 연결 |

| VDD18 | 42, 43 | P | Power | VDD18: Digital Power Supply (1.8 V) 1.8V 디지털 전원 이 두 핀은 함께 연결되어야 하고, 10uF 캐패시터로 GND에 연결되어야한다. |

| DGND | 19, 44, 47 | I | Power | DGND: Digital Ground 디지털 그라운드 |

| AGND | 2, 12 | I | Power | AGND: Analog Ground 아날로그 그라운드 |

| I1P I1N I2P I2N I3P I3N |

3 4 5 6 7 8 |

I | Analog | I1P: Positive Input for Analog ADC Channel I1N: Negative Input for Analog ADC Channel I2P: Positive Input for Analog ADC Channel I2N: Negative Input for Analog ADC Channel I3P: Positive Input for Analog ADC Channel I3N: Negative Input for Analog ADC Channel 전류용 센서의 +, - 핀 이 핀들은 아날로그 ADC채널을 위한 차동입력핀. 이 6가지의 아날로그 ADC 채널들은 맵핑을 통해서 유연하게 설정될 수 있다. 3.4 Analog/digital Channel Mapping. 참조 |

| Vref | 11 | O | Analog | Vref: Output Pin for Reference Voltage 기준 전압 출력 핀 This pin should be decoupled with a 4.7μF capacitor, it is better to add a 0.1μF ceramic capacitor. 이 핀은 4.7uF 캐패시터를 이용해서 디커플되어야하고 0.1uF 세라믹 캐패시터를 추가하는 것이 더 좋다. |

| V1P V1N V2P V2N V3P V3N |

13 14 15 16 17 18 |

I | Analog | V1P: Positive Input for Analog ADC Channel V1N: Negative Input for Analog ADC Channel These pins are differential inputs for analog ADC channel. 이 핀들은 아날로그 ADC 채널을 위한 차동 입력이다. These 6 analog ADC channels can be flexibly mapped, refer to 3.4 Analog/digital Channel Mapping. 이 6개의 아날로그 ADC 채널들은 유연하게 매핑이 될 수 있다. |

| Name | Pin No. | I/O | Type | Description |

| OSCI | 20 | I | OSC | OSCI: External Crystal Input 외부 크리스탈 입력 |

| OSCO | 21 | O | OSC | OSCO: External Crystal Output 외부 크리스탈 출력 16.348MHz 클리스탈이 OSCI과 OSCO 사이에 연결된다. 칩 내부에 두 개의 캐패시터가 있으므로 외부 캐패시터는 필요없다. |

| ZX0 ZX1 ZX2 |

22 23 24 |

O | LVTTL | ZX2/ZX1/ZX0:Zero-Crossing Output 제로크로싱 출력 이 핀들은 전압 또는 전류가 0을 지나갈 때 사용된다. 제로크로싱 모드는 ZXConfig 레지스터(07H)로 설정된다. |

| CF1 | 25 | O | LVTTL | CF1: (all-phase-sum total) Active Energy Pulse Output 유효에너지펄스출력(모든 상을 전부 합한닫.) |

| CF2 | 26 | O | LVTTL | CF2: (all-phase-sum total) Reactive/ Apparent Energy Pulse Output 무효/피상 에너지 펄스 출력, 모든 상의 전체 합 이 핀의 출력은 CF2varh 비트(MMode0의 b7) |

| CF3 | 27 | O | LVTTL | CF3: (all-phase-sum total) Active Fundamental Energy Pulse Output 유효 기본 에너지 펄스 출력 |

| CF4 | 28 | O | LVTTL | CF4: (all-phase-sum total) Active Harmonic Energy Pulse Output 하모닉 에너지 펄스 출력 |

| WarnOut | 29 | O | LVTTL | WarnOut: Fatal Error Warning 치명적인 에러 알리 이 핀은 측정된 파라미터의 체크섬 에러가 발생할 때 High가 된다. 그렇지 않으면 이 핀은 Low로 유지된다. Refer to 5.2.2 IRQ and WarnOut Signal Generation. |

| IRQ0 | 30 | O | LVTTL | IRQ0: Interrupt Output 0 인터럽트 출력 0 EMMIntState0 레지스터(1CCH)의 이벤트들이 하나 이상 발생할 때 사용된다. 해당 레지스터에 셋 된 비트가 없을 경우 해제된다. 검출 모드에서, IRQ0는 전류 검출의 출력을 표시한다. 검출 모드를 들어가거나 나올 때 IRQ0의 상태는 클리어 된다. |

| IRQ1 | 31 | O | LVTTL | IRQ1: Interrupt Output 1 인터럽트 출력 1 EMMIntState1 레지스터(1D0H)의 이벤트들이 하나 이상 발생할 때 사용된다. 해당 레지스터에 셋 된 비트가 없을 경우 해제된다. 검출 모드에서, IRQ1는 전류 검출의 출력을 표시한다. 검출 모드를 들어가거나 나올 때 IRQ1의 상태는 클리어 된다. |

| PM0 PM1 |

33 34 |

2 I |

LVTTL | PM1/0: Power Mode Configuration 전원 모드 설정 이 두핀은 표-2에서 설명한 전원 모드를 결정한다. |

| CS | 37 | 2 I |

LVTTL | CS: Chip Select (Active Low) 칩 선택(Low일 때 동작) SPI 모드에서, 읽기/쓰기를 할 때 마다 이 핀은 High에서 Low로 동작해야만 한다. 그리고 전체 동작에서는 Low로 유지되어야한다. |

| SCLK | 38 | 2 I |

LVTTL | SCLK: Serial Clock 시리얼 클럭 이 핀은 SPI 연결을 위한 클럭으로 사용한다. |

| SDO | 39 | O | LVTTL | SDO: Serial Data Output 시리얼 데이터 출력 이 핀은 SPI 모드를 위한 데이터 출력으로 사용된다. |

| SDI | 40 | 2 I |

LVTTL | SDI: Serial Data Input 시리얼 데이터 입력 SPI 모드의 시리얼 데이터 입력으로 사용된다. |

| TEST | 32 | I | LVTTL | 시스템 어플리케이션에서는 DGND에 연결되어 있어야한다. |

| IC | 9, 10, 36 | LVTTL | 시스템 어플리케이션에서 이 핀들은 DGND에 연결되어 있어야만 한다. | |

| NC | 35, 45, 46 | 이 핀들은 연결하지 않은 상태로 유지되어야만한다. | ||

| Note 1: The channel mapping is only valid in Normal mode and Partial Measurement mode. Note 2: All the digital input pins except OSCI are 5 V compatible. |

||||

3. 기능 설명

3.1 전원 공급

3.3V 단일 전원 사용. 내부 전압 레귤레이터로 1.8V를 만들고 이는 디지털 로직에 사용된다.

1.8V는 VDD18핀에 연결되어 있다. 외부 바이패스 캐패시터가 필요하다.

4개의 전원 모드가 있다.

- 일반모드(N 모드)

- 분할측정(M 모드)

- 검출(D 모드) : 1.8V 레귤레이터 OFF, 디지털 로직에 전원 공급이 되지 않는다. 검출모드 설정을 위한 검출 모드 관련 레지스터들(10H ~ 13H)을 제외하고 설정 레지스터의 값이 유지되지 않는다.

- 대기(Idle 모드)

검출 모드 또는 대기 모드에서부터 분할 측정, 일반 모드가 될 경우 모든 레지스터 설정 값들이 다시 설정되어야 한다.

3.2 Clock

외부 크리스탈을 직접 연결

OSCI 핀은 클럭 소스에 의해서 직접 동작 될 수 있다.

대기와 검출 전원 모드에서 오실레이터는 전원이 꺼질 것이다.

3.3 Reset

리셋 소스는

- 리셋 핀

- 전원 ON

- SoftReset 레지스터에 의해서 소프트웨어적으로 리셋이 발생함

3.3.1 Reset Pin

- 리셋 핀은 칩을 리셋 시키는데 사용될 수 있다. 리셋 핀은 RC 필터를 가지고 있고 I/O 핀 내의 2us의 일반적인 시간으로 구성된다. 일반적으로 2us의 글리치제거 필터와 같이 2us 보다 짧은 어떤 리셋 펄스들도 칩을 리셋 시킬 수 없다.

3.3.2 Power On Reset(POR)

전원이 입력되었을 때 POR 회로는 칩을 리셋 시킨다.

POR 회로는 다음과 같을 때 동작한다.

- DVDD 전원이 기준 전압을 넘어설 때

- VDD18 레귤레이터가 비활성화에서 활서화 될 때, 대기 또는 검출 모드에서 분할 측정

모드 또는 일반 모드로 변경될 때

3.3.3 Software Reset

일반 모드에서 칩은 SoftReset 레지스터에 쓰기를 하으로써 리셋 된다. 소프트웨어 리셋은 RESET 핀 또는 POR로부터 발생된 리셋의 범위와 동일하다. 이 세가지 리셋 소스는 같은 리셋 방법을 갖는다.

모든 디지털 로직과 레지스터, 리셋에서 빠지는 몇몇 특별한 레지스터를 제외하고,

- 연결로직 : 클럭 디바이더들

- 디지털 코어/로직 : 몇몇 특별한 레지스터들을 제외하고 모든 레지스터들

3.4 Analog/Digital Channel Mapping

아날로그 채널을 디지털 채널로 연결

6개의 아날로그 ADC 채널은 6개의 디지털 측정 채널에 유연하게 할당될 수 있다.

ChannelMapI, ChannelMapU 레지스터를 설정하는 것을 참조하라

채널 매핑은 일반 모드와 분할 측정 모드에서만 적용된다는 것에 주의하라.

3.5 측정 기능

MeterFn 비트들 중 어느 것이 셋 될 때 활성화 된다.

측정이 비활성화 되어 있을 때, CF 펄스는 발생되지 않고, 에너지 계산기는 에너지를 계산하지 않는다. 상태와 관련된 모든 에너지 계산은 클리어 될 것이다. 상태와 관련된 시작/무부하 처리 블록은 동작할 것이다.

계산된 에너지는 CF 핀에 펄스 주파수로 변경되고, 대응되는 에너지 레지스터에 저장된다.

3.5.1 에너지 레지스터들의 이론(이게 뭔 소린지 모르겠다.)

에너지 계산은 DSP 프로세서에 의해서 전력 값이 계산되고 1MHz 클럭 속도로 동작한다. 전력 계산 과정은 1us의 시간 변화에 대한 순시전력을 디지털 방식으로 적분하는 것과 같다.(?)

계산된 에너지는 CF펄스들을 사용하고 대응되는 내부 에너지 레지스터들을 사용한다.

계산된 에너지는 CF 펄스들의 주파수로 변환된다. 하나의 CF는 일반적으로 1kWh/MC에 대응된다.(MC는 측정 상수, e.g. 3200 imp/kWh) 그리고, 이 데이터 시트에서 일반적으로 에너지 단위로서 사용된다.(?) 계산과 변환에 대한 내부 에너지 분해능은 0.01CF이다.

0.01CF 펄스에너지 상수는 PL_상수처럼 사용된다.

0.01 CF이내, 진행과 역 에너지들은 틀어진다.(?) 에너지가 0.01 펄스를 넘어갈 때, 전진/역 에너지들 각각 증가한다.(?)

유효 에너지에 대한 예제들은 다음과 같다.

T0 : 순방향 에너지 레지스터가 12.34펄스이고 역방향 에너지 레지스터가 1.23 펄스

t0 ~ t1 :

3.5.2 Energy Registers

이 칩은 분할되지 않은 유효, 무효 피상 에너지를 측정한다. 유효 기본과 고조파 에너지를 분할하는 것 처럼(?). 레지스터들은 아래와 같다.

3.5.2.1 Total Energy Registers 전체 에너지 레지스터

각 상과 모든 상의 합은 다음 레지스터들이 있다.

- 유효 순방향/역방향

- 무효 순방향/역방향

- 순시 에너지

전부 20개의 에너지 레지스터들이 있다. 레지스터들은 5.5.1 표준 에너지 레지스터들에 정의 되어 있다.

3.5.2.2 Fundamental and Harmonic Energy Registers 기본과 고조파 에너지 레지스터들

유효전력은 기본과 고조파 에너지로 분할 된다. 무효전력은 분할 되지 않는다. 기본과 고조파 에너지는 레지스터들에 대해 앞서 설명된 유효전력 계산하는 방법과 같이 계산된다.

- 기본과 고조파

- 모든 상의 합/ 상 A/상 B/상 C

- 순방향/역방향(지상? 진상?)

총 16개의 레지스터가 있다. 5.5.2 Fundamental / Harmonic Energy Register를 확인하라.

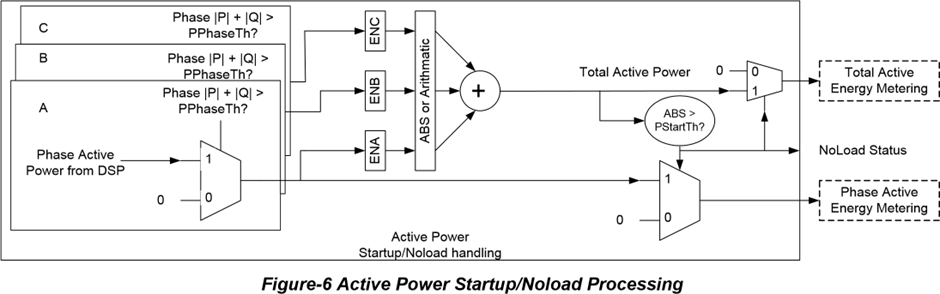

3.5.4 Startup And No-Load Power

시작 전력 한계치 레지스터가 있다.(PStartTh(35H)) 5.4절 설정과 교정 레지스터들 참조

전력 한계치(power threshold) 레지스터는 모든 상의 합 유효, 무효, 피상 전력을 위해 정의된다.

대응되는 모든 상의 전력 합이 시작 한계치 보다 클 때 계측이 시작된다.

전력 값이 시작 한계치 보다 작을 때, 에너지는 계산되지 않고, 무부하 상태로 인식된다.

3상의 각각에 대하여 유효, 무효, 피상 에너지를 측정하는데 사용되는 무부하 전류 한계치 레지스터가 있다.

만약 |P|+|Q|가 대응되는 전력 한계치보다 낮으면, 측정 위상은 계산되지 않는다. PStartTH 레지스터와 다른 한계치 레지스터들을 참조하라.

무부하 상태를 나타내는 무부하 상태 비트들이 있다.(TPnoload/TQnoload 비트들, 기본/고조파 에너지 레지스터의 b14 ~15)

무부하 상태에서는 펄스의 출력이 없다. 전원 온 상태는 무부하 상태이다.

DSP로부터 계산된 유효전력은 해당 상의 |P|+|Q|가 PPhaseTh보다 클 때 계산된다. 아니면 0이 계산된다.

3.6 측정 기능

측정 파라미터는 다음의 8가지로 분리 될 수 있다.

- 유효/무효/피상 전력

- 기본/고조파 전력

- 전압/전류의 RMS값

- 역율(PF)

- 위상각

- 주파수

- 온도

- 피그 값

측정된 파라미터는 온도를 제외하고 16 위상 전압 사이클 동안의 평균 값이다.(50Hz에서 약 320ms 가 소요된다. 이 측정된 파라미터는 약 3Hz로 갱신된다. 표 17을 확인하라.

3.6.1 유효/무효/피상전력

유효/무효/피상 전력 측정 레지스터는 다음과 같이 분류된다.

- 유효, 무효, 피상전력

- 모든 위상의 합/위상 A/위상 B/위상 C

전부 12개의 전력 레지스터가 있다. 전력과 역율 레지스터들을 검토하라.

각 위상의 피상 전력은 그 위상의 Vrms와 Irms 측정의 곱으로 결정된다.

모든 위상 합 전력은 각 위상의 측정된 전력의 수학적인 합이다. 위상들의 합은 MMode0 레지스터에 의해 설정된다.

3.6.2 기본/고조파 유효 전력

기본/고조파 유효 전력 측정 레지스터는 아래와 같이 분류된다.

- 기본과 고조파 전력

- 모든 위상의 합/위상 A/위상 B/위상 C

모두 8개의 전력 레지스터가 있다. 5.6.2 절을 참조하라

3.6.3 역율(Mean Power Factor)

다음에 대해서 역율이 결정된다. 모든 위상의 합/위상 A/위상 B/위상 C

전부 4개의 역율 레지스터들이 있다. 5.6.1절을 참조하라.

각 모든 위상에 대해서

PF_ALL= All_phase_ sum active_powerAll_phase_ sum apparent_power

각 위상에 대해서

PF_phase= active_powerapparent_power

3.6.4 전압/전류 실효치

전압/전류 RMS 레지스터는 다음과 같이 나뉠 수 있다.

각 상에 대해서 위상 A, 위상 B, 위상 C의 전압/전류

중성선의 전류 RMS

중성선의 전류는 동시에 계산될 수 있다.

iN=iA+iB+iC

전부 7개의 RMS 레지스터가 있다.

5.6.2절을 참조하라.

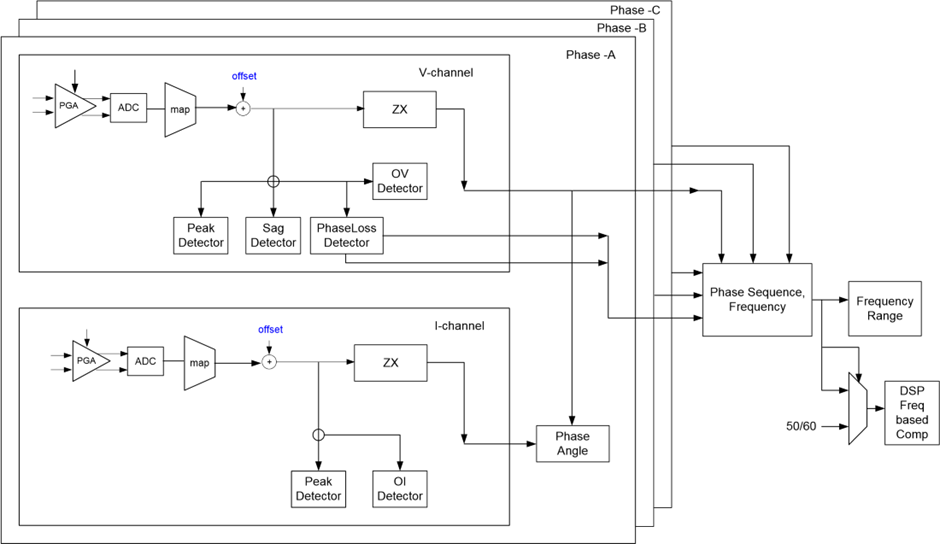

3.6.5 위상각

위상각 측정 레지스터는 다음과 같이 나뉘어 질 수 있다.

- 위상 A, 위상 B, 위상 C

- 전압/전류

모두 6개의 레지스터들이 있다.5.6.3을 참조하라

위상각은 같은상의 전압과 전류 사이의 시간에 의해서 측정된다.

3.6.6 주파수

주파수는 전압 채널의 제로크로싱 지점으로 계산된다.

위상 A 전압 신호 제로크로싱은 주파수를 위해서 사용된다. 만약 위상 A가 SAG 조건이면, 위상 C가 사용될 것이다. 만약 위상 C가 또 SAG 조건이면 위상 B가 사용될 것이다.

만약 모든 위상이 SAG 조건이면, 주파수는 위상 손실 조건이 아닌 채널을 이용해서 측정될 것이다. 만약 모든 위상이 손실 상태이면, 주파수는 0이 될 것이다.

주파수 데이터는 평균이 아니라 각 사이클 마다 갱신된다. 5.6.3절을 참조하라.

3.6.7 온도

칩 내부의 온도는 대략 100ms 마다 칩 내부의 온도센서에 의해 측정된다. 5.6.3절을 참조하라.

3.6.8 피크 값

모두 6개의 피크값 레지스터가 있다. 5.6.3절, 3.7.1절을 참조하라.

3.6 측정 기능

측정 파라미터는 다음의 8가지로 분리 될 수 있다.

- 유효/무효/피상 전력

- 기본/고조파 전력

- 전압/전류의 RMS값

- 역율(PF)

- 위상각

- 주파수

- 온도

- 피그 값

측정된 파라미터는 온도를 제외하고 16 위상 전압 사이클 동안의 평균 값이다.(50Hz에서 약 320ms 가 소요된다. 이 측정된 파라미터는 약 3Hz로 갱신된다. 표 17을 확인하라.

3.6.1 유효/무효/피상전력

유효/무효/피상 전력 측정 레지스터는 다음과 같이 분류된다.

- 유효, 무효, 피상전력

- 모든 위상의 합/위상 A/위상 B/위상 C

전부 12개의 전력 레지스터가 있다. 전력과 역율 레지스터들을 검토하라.

각 위상의 피상 전력은 그 위상의 Vrms와 Irms 측정의 곱으로 결정된다.

모든 위상 합 전력은 각 위상의 측정된 전력의 수학적인 합이다. 위상들의 합은 MMode0 레지스터에 의해 설정된다.

3.6.2 기본/고조파 유효 전력

기본/고조파 유효 전력 측정 레지스터는 아래와 같이 분류된다.

- 기본과 고조파 전력

- 모든 위상의 합/위상 A/위상 B/위상 C

모두 8개의 전력 레지스터가 있다. 5.6.2 절을 참조하라

3.6.3 역율(Mean Power Factor)

다음에 대해서 역율이 결정된다. 모든 위상의 합/위상 A/위상 B/위상 C

전부 4개의 역율 레지스터들이 있다. 5.6.1절을 참조하라.

각 모든 위상에 대해서

PF_ALL= All_phase_ sum active_powerAll_phase_ sum apparent_power

각 위상에 대해서

PF_phase= active_powerapparent_power

3.6.4 전압/전류 실효치

전압/전류 RMS 레지스터는 다음과 같이 나뉠 수 있다.

각 상에 대해서 위상 A, 위상 B, 위상 C의 전압/전류

중성선의 전류 RMS

중성선의 전류는 동시에 계산될 수 있다.

iN=iA+iB+iC

전부 7개의 RMS 레지스터가 있다.

5.6.2절을 참조하라.

3.6.5 위상각

위상각 측정 레지스터는 다음과 같이 나뉘어 질 수 있다.

- 위상 A, 위상 B, 위상 C

- 전압/전류

모두 6개의 레지스터들이 있다.5.6.3을 참조하라

위상각은 같은상의 전압과 전류 사이의 시간에 의해서 측정된다.

3.6.6 주파수

주파수는 전압 채널의 제로크로싱 지점으로 계산된다.

위상 A 전압 신호 제로크로싱은 주파수를 위해서 사용된다. 만약 위상 A가 SAG 조건이면, 위상 C가 사용될 것이다. 만약 위상 C가 또 SAG 조건이면 위상 B가 사용될 것이다.

만약 모든 위상이 SAG 조건이면, 주파수는 위상 손실 조건이 아닌 채널을 이용해서 측정될 것이다. 만약 모든 위상이 손실 상태이면, 주파수는 0이 될 것이다.

주파수 데이터는 평균이 아니라 각 사이클 마다 갱신된다. 5.6.3절을 참조하라.

3.6.7 온도

칩 내부의 온도는 대략 100ms 마다 칩 내부의 온도센서에 의해 측정된다. 5.6.3절을 참조하라.

3.6.8 피크 값

모두 6개의 피크값 레지스터가 있다. 5.6.3절, 3.7.1절을 참조하라.

3.7 전력 품질 모니터링

3.7.1 순시 시그널 모니터링

피크 검출 기능 : 각 채널의 피크 값은 PeakDet_period 비트의 설정에 의한 시간 주기 내에 검출 된다.(SagPeakDetCfg의 b15 ~ 8)

검출된 피크 값은 교차 주기마다 갱신된다.

레지스터들 : 검출된 피크 값은 U/I 피크 레지스터를 이용해서 제어된다. 5.6.3절을 참조하라.

3.7.2 상태와 이벤트들에 관련된 순시 시그널

3.7.2.1 SAG 검출

3.7.2.2 위상 손실 검출

3.7.2.3 과전압(OV) 검출

3.7.2.4 과전류(OI) 검출

3.7.3 상태와 이벤트들에 관련된 주파수 모니터링

3.7.4 제로크로싱 검출

제로크로싱 검출기는 3개의 위상 각각에 대한 전압/전류의 기본 주파수의 0점 포인트를 검출한다.

6.5절을 참조하라.

제로크로싱 신호는 독립적으로 설정되고 출력될 수 있다. ZXConfig 레지스터의 정의를 참조하라.

3.7.6 위상 순서 에러 검출

위상 순서는 두 가지 경우에 대해 검출된다. 3P4W, 3P3W, 이것은 MMode0의 b8인 3P3W에 의해 결정된다.

3P4W일 경우,

순서 수정 ; 전압/전류 제로크로싱 시퀀스는 위상 A, 위상 B, 위상 C

3P3W일 경우

순서 수정 : 전압/전류 제로크로싱은 A와 C 위상 사이가 180도 보다 크다. 이 기준이 위배되었을 경우, 위상 순서 에러이다. URevWnST 비트(EMMState0의 b9) 또는 IRevWnST 비트(EMMState0의 b8)가 셋 된다.

3.8 파워모드

4개의 파워모드들이 있다. 파워모드는 PM1, PM0핀에 의해 하나로 설정된다.

| PM1:PM0 Value | Power Mode |

| 11 | Normal (N mode) |

| 10 | Partial Measurement (M mode) |

| 01 | Detection (D mode) |

| 00 | Idle (I mode) |

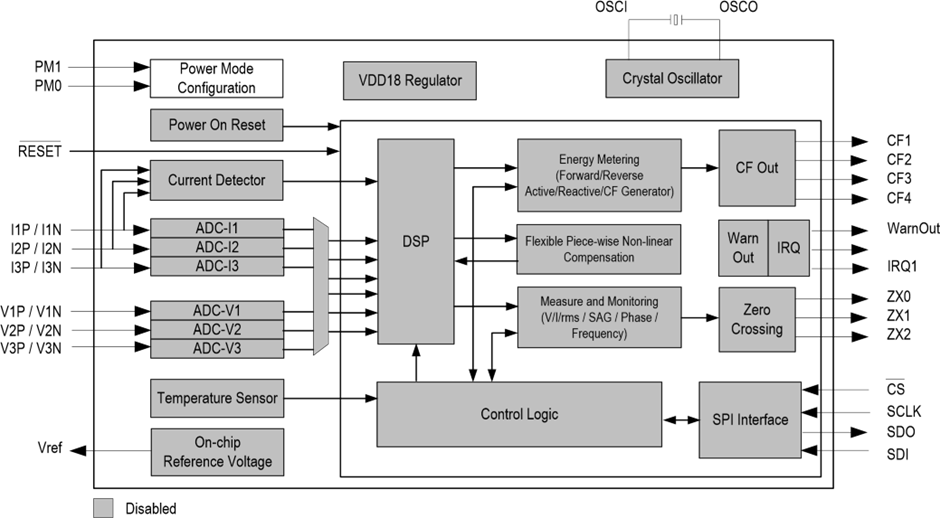

3.8.1 일반모드(N모드)

일반 모드에서, 기본은 전류 검출 블록을 제외하고 모든 기능 블록들이 활성화 되는 것이다. 그림 10을 참조하라.

일반 모드에서 DetectCtrl레지스터 내의 제어 비트를 이용해서 전류 검출은 활성화 될 수 있고, 교정될 수 있다.

3.8.2 IDLE모드(I 모드)

아이들 모드에서 , 모든 기능들은 셧오프 된다.

아날로그 블록들의 전원이 공급되나 회로들은 파워다운 모드로 들어간다. 즉 전원은 공급되나 모든 전류 패스들이 셧-오프 된다. 이 모드에서는 매우 낮은 디바이스 리키지가 생길 수 있기 때문에 매우 적은 전류가 흐를 수 있다. 디지털 I/O들은에는 전원이 공급된다.

I/O와 아날로그 연결에서, 디지털 포어(전원이 공급되지 않은) 디지털 코어로부터 입력된 신호들은 표-3에서 설명된 것과 같이 알려진 상태로 설정될 것이다.(?????)

PM1과 PM0핀들은 외부 MCU에의해 제어되고 활성화 된다. 그리고 다른 모드들로 설정될 수 있다.

디지털 I/O가 셧오프가 안되었기 때문에 I/O 회로는 아이들 모드에서도 활성화 되어 있음을 주의하라. 어플리케이션은 I/O에 공급되는 유효한 로직 레벨을 확실시 해야 한다.

표-3은 아이들 상태의 디지털 I/O와 전원 핀들의 상태를 보여준다. 출력을 위한 입력들과 출력들에 대한 요구사항을 보여 준다. (?)

3.8.3 검출모드(D 모드)

검출 모드에서, 전류 검출이 가능하다. 전류 검출은 어떤 위상 전류가 설정된 한계치를 넘어가는지를 저전력 비교기를 이용해서 비교한다.

하나 또는 여러 개의 상의 전류가 설정된 한계치를 넘어가면, IRQ0 핀을 High로 만들고 파워도드가 변경될 때까지 유지한다. IRQ0 상태는 검출 모드를 들어가거나 빠져나올 때 클리어 된다.

모든 세개의 전류 채널의 전류가 설정된 한계점을 넘어서면, IRQ1은 High로되고 전원 모드가 변경 될 때 까지 유지된다. IRQ1 상태는 검출 모드로 들어가거나 탈출 할 때 클리어 된다.

검출 모드로 진입하기 전에 한계치 레지스터들은 일반 모드에서 프로그램 된다.

디지털 I/O 상태는 아이들 상태일 때와 동일하다.( IRQ0/IRQ1과 PM1/PM0를 제외하고)

각상의 양과 음의 전류를 검출하기 위해서 두 개의 비교기를 가지고 있다. 각 비교기의 한계치는 개별적으로 설정될 수 있다. 두개의 비교기는 기본적으로 활성화 되어 있고, 양측 검출이라 불린다. 사용자는 또한 전력 소비 저장을 위해 단지 하나의 비교기만 활성화 시킬 수 있다. 이를 한쪽 검출이라 부른다.

양쪽 검출은 응답이 더 빠르고 반파 전류를 검출할 수 있다. 그러나 한쪽 검출 보다 거의 두 배에 달하는 전력을 소비한다.

비교기들은 DetectCtrl레지스터를 설정함으로서 파워다운이 될 수 있다. 전류 검출은 DetectCtrl 레지스터의 제어비트를 사용해서 일반 모드에서 활성화 될 수 있고, 교정될 수 있다.

3.8.4 분할 측정모드 (M 모드)

이 모드에서는 모든 측정들은 일반 모드에서 측정하는데 사용되는 같은 하드웨어를 사용한다. 전력을 줄이기 위해서, 에너지 계산기 블록과 DSP 계산 코드의 부분은 이 모드에서는 동작하지 않는다.

이 모드에서, 어플리케이션에서 요구하는 저전력을 만들기 위해서 PMPwrCtrl 레지스터의 설정 비트들이 있다.

- 전압과 전력을 측정할 필요가 없는 세개의 아날로그 채널을 끄기 위한 옵션

- 16.384MHz에서 8.192MHz로 디지털 클럭을 줄이는 옵션

부분 측정 모드에서, CRC 체크는 비활성화 된다. 이 인터럽트들은 발생하지 않는다.

3.8.5 파워모드들의 변경

5초è검출모드è전류값이 기준을 넘으면 MCU에 신호를 보내고è 60초 후에 분할 측정모드è

위의 파워모드들은 PM0와 PM1 핀에 의해 제어된다. 어플리케이션에서, PM0, PM1은 외부 MCU에 연결된다. PM0, PM1핀은 내부 RC-필터들을 가지고 있다.

일반적으로, 정전 시간의 대부분은 아이들모드이다. MCU에 의해서 제어되고 일정 시간(예를 들어 5초)이 지나야 검출 모드로 들어간다. 만약 전류가 설정된 한계치를 넘게 되면 MCU에 정보를 보낸다. 전류에 관련된 읽기를 위한 특정 간격(60초)에서 분할 측정모드로 들어가도록 명령을 보낸다. 전류를 읽은 후에 다시 아이들 모드가 된다.

측정된 전류는 몇몇 측정 모델에 따라 에너지를 계산하는데 사용이 된다.(전류 RMS를 전압과 곱해서 전력을 계산하는데)

다른 파워모드 변경은 아이들 모드를 통해서 진행된다. 그림 14를 확인하라.

3.9 외부 요소 보상

교정된 채널의 이득과 위상 딜레이 옵셋은 어떤 기준 값에 대해서 교정이 된다. 이 특징은 외부 요소가 이상적이지 않고 저가의 센서가 사용된 시스템에서 유용하다.

세가지 기준 파라미터가 있다.

- 측정된 전류 RMS(각 위상별)

- 측정된 라인 주파수(모든 위상에 공통)

- 측정된 온도

보상을 위한 두 가지의 파라미터가 있다.

- 채널 이득 보상

- 채널 위상 딜레이 보상

다음은 보상대응이다.

- 측정된 전류 RMS는 각 상당이다. 각 상에 대해서 Igain와 Phi가 된다.???

- 이것은 전류 트랜스포머와 같은 전류센서의 비선형을 보상하는 방법이다. 비 선형성은 이득이 비선형이거나 위상이 비선형일 수 있다. 이득이 비선형인 것은 Igain 보상에의해 보상되고, 위상의 비선형성는 위상보상에 의해서 보상된다.

- 주파수 보상은 단지 Phi/Delay로 간다.(모든 위상이 같다)

- 온도 보상은 단지 UGain으로 간다.(각 상에 대해서???)

Table-4 Compensation Related Registers

| Parameter | Describtion | Registers |

| LogIrms | Measured Current RMS | LOGIrms0, LOGIrms1 |

| F0 | Nominal line frequency | F0 |

| T0 | Nominal temperature | T0 |

| GainIrms | Gain compensation for Irms | GainAIrms01, GainAIrms2, GainBIrms01, GainBIrms2, GainCIrms01, GainCIrms2 |

| PhiIrms | Phase compensation for Irms | PhiAIrms01, PhiAIrms2, PhiBIrms01, PhiBIrms2, PhiCIrms01, PhiCIrms2 |

| UGainT | Temperature compensation only goes to UGain | UGainTAB, UGainTC |

| PhiF | Frequency compensation only goes to Phi/Delay | PhiFreqComp |

4. SPI Interface

4.1 Interface 설명

4 핀이 아래와 같이 연결에 사용된다.

SDI : 데이터 핀, 입력

SDO : 데이터핀, 출력

SCLK : 클럭 입력 핀

CS : 칩 선책 핀 입력

4.2 SPI Interface

그림 16은 슬레이브모드로 동작하는 연결을 보여준다.

4.2.1 SPI 슬레이브 연결 포맷

SPI 모드에서, SDI의 데이터는 SCLK의 상승 에지에서 칩으로 시프트되어진다. 반면에 SCLK의 하강에지에서 SDO 데이터가 칩으로부터 출력된다.

타이밍도를 위해서 그림 17, 그림 18을 참조하라.

접속 형태

SDI의 첫 비트는 아래와 같이 접속 형태를 결정한다.

| Instruction | Description | Instruction Format |

| Read | read from registers | 1 |

| Write | write to registers | 0 |

어드레스

접속 형태 비트 다음의 고정된 15비트이다. 하위 10비트는 어드레스로 사용되고, 상위 5비트는 “Don’t Care”이다.

4.2.2 신뢰성향상기능

SPI 읽기/쓰기 동작은 CS가 Low일 때 정의 된다. 각 동작은 하나의 레지스터에 접근할 수 있다. 각 CS가 Low일 때 동작이 결정된다.

쓰기 : CS가 Low에서 High가 될 때 접근이 이루어지고, CS가 Low일 때 정확히 32 SCLK 사이클이 수신 되어야 한다.

읽기 : 만약 SCLK가 16이상(전체 어드레스가 수신되었을 때), 데이터는 내부 레지스터로부터 읽혀지고 SDO 핀으로 이동한다. 그리고, LastSPIData레지스터가 갱신된다. R/C레지스터?들은 LastSPIData 레지스터가 갱신된 뒤에만 클리어 된다.

'임베디드' 카테고리의 다른 글

| ATMEL M90E32AS 실험 결과 (0) | 2023.08.24 |

|---|---|

| Atmel M90E32 제어 (0) | 2023.06.22 |

| ADS131M02 SPI Communication words (0) | 2023.06.19 |

| 24C02 clock Timing 맞추기 (0) | 2023.04.26 |

| 시리얼 통신 모니터링 (0) | 2023.01.18 |